Numa: различия между версиями

Sirmax (обсуждение | вклад) (→Linux) |

Sirmax (обсуждение | вклад) (→Linux) |

||

| Строка 106: | Строка 106: | ||

Платформа/Материнская Плата |

Платформа/Материнская Плата |

||

|style="width: 45%" | |

|style="width: 45%" | |

||

| + | <BR> |

||

<PRE> |

<PRE> |

||

System Information |

System Information |

||

Версия 15:29, 3 апреля 2024

Numa

Это заготовка перевода статьи про Numa

с некоторыми моими дополнениями и уточнениями

Можно ли использовать один CPU в многопроцессорных системах? (и почему)

Почему возникает такой вопрос?

По-тому что системы с 2 и более сокетами на материнской плате допускают возможное расширение без полной замены сервера

Ответ на вопрос - "Да, работать будет", но с некоторыми оговорками.

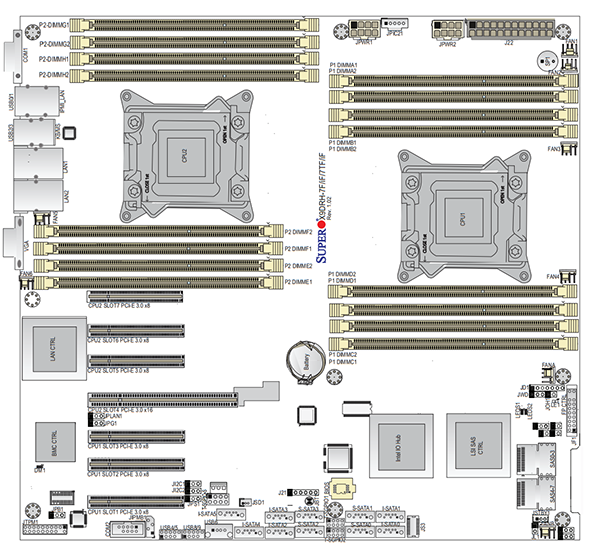

Supermicro X8DTN

Подавляющее большинство материнских плат «просто работают»,

если вы поставить процессор в сокет с наименьшим номером

Это справедливо как для материнских плат Intel, так и для AMD в целом, а в случае сомнения информацию можнонайти в руководстве (но у меня никогда таких сомнений не было)

Вот пример материнской платы Supermicro X8DTN, которая представляла собой довольно двухпроцессорную плату Xeon серий Intel 5500 и 5600.

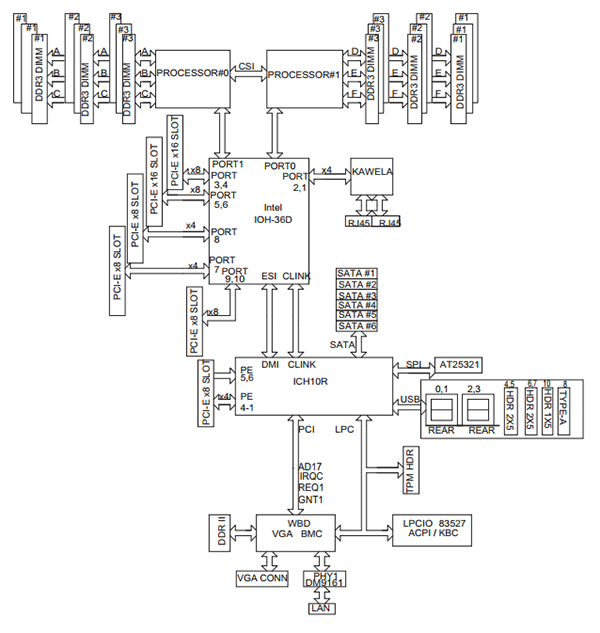

Dell C6100

Поскольку наборы микросхем Intel серий 5500 и 5520 имели северный мост IOH,

установка только одного процессор в двухпроцессорной материнской плате не привела к недоступности каких-то ресурсов материнской платы.

За исключением памяти, так как каждый слот памяти относится к одному из процессоров

Во времена Intel LGA1366, а также на платформах AMD C32 и G34 и северный, и южный мосты находились на материнской плате,

поэтому процессоры обычно подключались через северный мост, чтобы получить доступ к шине PCI.

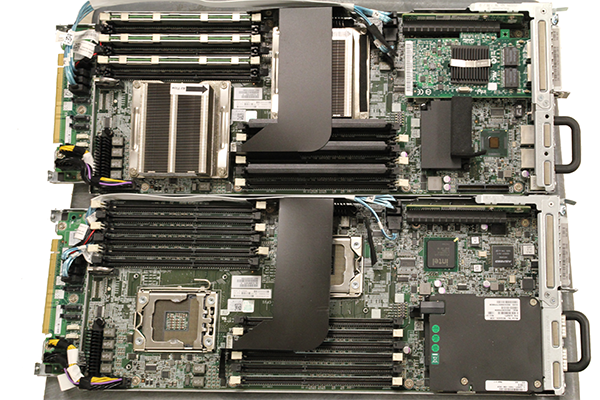

В качестве примера можно рассмотреть Dell C6100 (это такой а-ля блейд, 4 ноды в корпусе 2U с общими резервированными блоками питания но каждый со своими дисками и сетью)

C установкой одного процессора и заполнением только половины слотов памяти он будет работать как обычная однопроцессорная система

На фото в примере можно видеть что установлен только один процессор и заполнена только половина слотов DIMM, соответствующих установленному процессору.

Эта конфигурация значительно отличается от более современных систем тспользующих сокет LGA2011

В качестве примера более новой конфигурации рассмотрим плату Supermicro X9DRH-7TFу которой есть onboard LSI SAS и стевая карта 10GbE Intel X540.

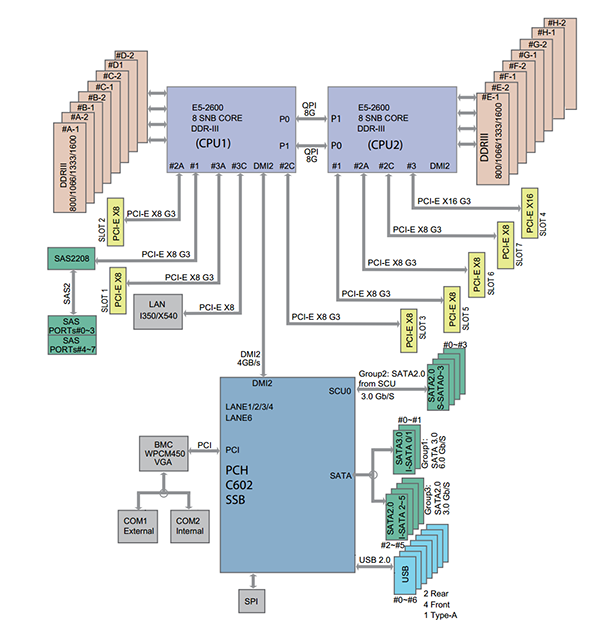

Supermicro X9DRH-7TF

Более свежие архитектуры добавляют еще один уровень сложности.

На примере двухпроцессорной платформы Intel Xeon E5 LGA2011 слоты расширения PCIe напрямую привязаны к процессору.

На изображении выше можно увидеть каждый слот PCIe, привязанный к определенному процессору.

Когда сокет CPU не заполнен, часть линий PCIe оказываются "подвешенными в воздухе".

Это оказывает существенное влияние на функциональность материнской платы.

Например, если второй разъем CPU не заполнен на материнской плате с двумя разъемами,

часть устройств встроенных в платк как, например, контроллеры Ethernet и SAS, не будут работать.

(Примечание: но это теория, на практике обычно нельзя поставить только второй процессор, а встроенные устройства (соответствующие им линии PCIe) подключены к первому (или нулевому, зависит от нумерации) процессору. )

Кроме того, как уже сказано, часть линий PCIe могут будут работать что сделает слоты бесполезными.

Вот соответствующая диаграмма для материнской платыSupermicro X9DRH-7TF:

Здесь мы видим, что если бы CPU1 отсутствовал (гипотетический случай),

то линии PCIe встроенных контроллеров Intel X540 10GbE LAN и LSI SAS2208 оказались бы "висящими в воздухе" (никуда не подключены).

C другой стороны без CPU2 (это уже более реальный случай) не будет доступа к нескольким слотам PCIe 3.0 x8.

К счастью, большинство производителей материнских плат указывают в своих руководствах соответвие между процессорными сокетами и слотами PCIe

Linux

|

Описание ячейки |

|

|

|---|---|---|

|

Платформа/Материнская Плата |

System Information

Manufacturer: HP

Product Name: ProLiant DL180 G6

Version:

Serial Number: CZJ0220BHZ

UUID: 01245e64-8efe-d511-b3f4-d8d385e535ec

Wake-up Type: Power Switch

SKU Number: 470065-095

Family:

|

Base Board Information

Manufacturer: Supermicro

Product Name: X9DRW

|

|

Просмотр информации о "железе" |

numactl --hardware available: 2 nodes (0-1) node 0 cpus: 0 1 2 3 4 5 12 13 14 15 16 17 node 0 size: 96691 MB node 0 free: 58301 MB node 1 cpus: 6 7 8 9 10 11 18 19 20 21 22 23 node 1 size: 96728 MB node 1 free: 66809 MB node distances: node 0 1 0: 10 20 1: 20 10 |

numactl --hardware available: 2 nodes (0-1) node 0 cpus: 0 1 2 3 4 5 12 13 14 15 16 17 node 0 size: 32154 MB node 0 free: 31402 MB node 1 cpus: 6 7 8 9 10 11 18 19 20 21 22 23 node 1 size: 32204 MB node 1 free: 31733 MB node distances: node 0 1 0: 10 21 1: 21 10

|

|

Просмотр статистики использования: |

numastat

node0 node1

numa_hit 52314463 58897099

numa_miss 0 0

numa_foreign 0 0

interleave_hit 28279 28251

local_node 52312978 58861619

other_node 1485 35480

|

numastat

node0 node1

numa_hit 945918 557506

numa_miss 0 0

numa_foreign 0 0

interleave_hit 16862 16657

local_node 944697 538529

other_node 1221 18977

|

|

|

Machine (189GB total)

Package L#0

NUMANode L#0 (P#0 94GB)

L3 L#0 (12MB)

L2 L#0 (256KB) + L1d L#0 (32KB) + L1i L#0 (32KB) + Core L#0

PU L#0 (P#0)

PU L#1 (P#12)

L2 L#1 (256KB) + L1d L#1 (32KB) + L1i L#1 (32KB) + Core L#1

PU L#2 (P#1)

PU L#3 (P#13)

L2 L#2 (256KB) + L1d L#2 (32KB) + L1i L#2 (32KB) + Core L#2

PU L#4 (P#2)

PU L#5 (P#14)

L2 L#3 (256KB) + L1d L#3 (32KB) + L1i L#3 (32KB) + Core L#3

PU L#6 (P#3)

PU L#7 (P#15)

L2 L#4 (256KB) + L1d L#4 (32KB) + L1i L#4 (32KB) + Core L#4

PU L#8 (P#4)

PU L#9 (P#16)

L2 L#5 (256KB) + L1d L#5 (32KB) + L1i L#5 (32KB) + Core L#5

PU L#10 (P#5)

PU L#11 (P#17)

Package L#1

NUMANode L#1 (P#1 94GB)

L3 L#1 (12MB)

L2 L#6 (256KB) + L1d L#6 (32KB) + L1i L#6 (32KB) + Core L#6

PU L#12 (P#6)

PU L#13 (P#18)

L2 L#7 (256KB) + L1d L#7 (32KB) + L1i L#7 (32KB) + Core L#7

PU L#14 (P#7)

PU L#15 (P#19)

L2 L#8 (256KB) + L1d L#8 (32KB) + L1i L#8 (32KB) + Core L#8

PU L#16 (P#8)

PU L#17 (P#20)

L2 L#9 (256KB) + L1d L#9 (32KB) + L1i L#9 (32KB) + Core L#9

PU L#18 (P#9)

PU L#19 (P#21)

L2 L#10 (256KB) + L1d L#10 (32KB) + L1i L#10 (32KB) + Core L#10

PU L#20 (P#10)

PU L#21 (P#22)

L2 L#11 (256KB) + L1d L#11 (32KB) + L1i L#11 (32KB) + Core L#11

PU L#22 (P#11)

PU L#23 (P#23)

HostBridge

PCIBridge

PCI 0a:00.0 (Ethernet)

Net "enp10s0f0"

PCI 0a:00.1 (Ethernet)

Net "enp10s0f1"

PCIBridge

PCI 09:00.0 (RAID)

Block(Disk) "sdf"

Block(Disk) "sdd"

Block(Disk) "sdb"

Block(Disk) "sdg"

Block(Disk) "sde"

Block(Disk) "sdc"

Block(Disk) "sda"

Block(Disk) "sdh"

PCIBridge

PCIBridge

PCIBridge

PCI 08:00.0 (Ethernet)

Net "enp8s0f0"

PCI 08:00.1 (Ethernet)

Net "enp8s0f1"

PCIBridge

PCI 07:00.0 (Ethernet)

Net "enp7s0f0"

PCI 07:00.1 (Ethernet)

Net "enp7s0f1"

PCIBridge

PCI 04:00.0 (Storage)

PCIBridge

PCI 02:00.0 (VGA)

PCI 00:1f.2 (SATA)

Block(Disk) "sdi"

|

lstopo

Machine (63GB total)

Package L#0

NUMANode L#0 (P#0 31GB)

L3 L#0 (15MB)

L2 L#0 (256KB) + L1d L#0 (32KB) + L1i L#0 (32KB) + Core L#0

PU L#0 (P#0)

PU L#1 (P#12)

L2 L#1 (256KB) + L1d L#1 (32KB) + L1i L#1 (32KB) + Core L#1

PU L#2 (P#1)

PU L#3 (P#13)

L2 L#2 (256KB) + L1d L#2 (32KB) + L1i L#2 (32KB) + Core L#2

PU L#4 (P#2)

PU L#5 (P#14)

L2 L#3 (256KB) + L1d L#3 (32KB) + L1i L#3 (32KB) + Core L#3

PU L#6 (P#3)

PU L#7 (P#15)

L2 L#4 (256KB) + L1d L#4 (32KB) + L1i L#4 (32KB) + Core L#4

PU L#8 (P#4)

PU L#9 (P#16)

L2 L#5 (256KB) + L1d L#5 (32KB) + L1i L#5 (32KB) + Core L#5

PU L#10 (P#5)

PU L#11 (P#17)

HostBridge

PCIBridge

PCI 02:00.0 (Ethernet)

Net "eno1"

PCI 02:00.1 (Ethernet)

Net "eno2"

PCIBridge

PCI 04:00.0 (Ethernet)

Net "enp4s0f0"

PCI 04:00.1 (Ethernet)

Net "enp4s0f1"

PCIBridge

PCI 07:00.0 (SAS)

PCIBridge

PCIBridge

PCIBridge

PCIBridge

PCI 0c:00.0 (VGA)

PCI 00:1f.2 (SATA)

Block(Disk) "sdd"

Block(Disk) "sdb"

Block(Disk) "sdc"

Block(Disk) "sda"

Package L#1

NUMANode L#1 (P#1 31GB)

L3 L#1 (15MB)

L2 L#6 (256KB) + L1d L#6 (32KB) + L1i L#6 (32KB) + Core L#6

PU L#12 (P#6)

PU L#13 (P#18)

L2 L#7 (256KB) + L1d L#7 (32KB) + L1i L#7 (32KB) + Core L#7

PU L#14 (P#7)

PU L#15 (P#19)

L2 L#8 (256KB) + L1d L#8 (32KB) + L1i L#8 (32KB) + Core L#8

PU L#16 (P#8)

PU L#17 (P#20)

L2 L#9 (256KB) + L1d L#9 (32KB) + L1i L#9 (32KB) + Core L#9

PU L#18 (P#9)

PU L#19 (P#21)

L2 L#10 (256KB) + L1d L#10 (32KB) + L1i L#10 (32KB) + Core L#10

PU L#20 (P#10)

PU L#21 (P#22)

L2 L#11 (256KB) + L1d L#11 (32KB) + L1i L#11 (32KB) + Core L#11

PU L#22 (P#11)

PU L#23 (P#23)

|